Pada post sebelumnya telah disampaikan bagaimana PSIM dipergunakan untuk menjelaskan unjuk kerja masing-masing komponen di rangkaian SEPIC. Di artikel yang sama itu pula telah disampaikan beberapa alternatif sakelar dan cara pemicuannya. Di artikel sebelumnya lagi, LTspice telah dipakai untuk menjelaskan kondisi rangkaian SEPIC pada saat sakelar hidup dan pada saat sakelar mati.

Di artikel ini akan dicoba untuk mempergunakan LTspice sebagai pengganti PSIM untk melakukan simulasi. Akan diperlihatkan adanya perbedaan pengaturan antara LTspice dan PSIM, misalnya tentang konvensi tanda. Juga kali ini akan mulai diperlihatkan bagaimana simulasi dengan menggunakan model SPICE komponen nyata, yang bukan merupakan model ideal. Sekalipun model ini pun tidak akan memiliki karakteristik dan unjuk kerja yang persis sama dengan komponen fisiknya, tetapi model komponen akan jauh lebih mendekati untuk masing-masing tipe komponen daripada model yang ideal. Sebagai catatan, PSIM sebenarnya sudah memberikan fasilitas untuk melakukan simulasi dengan model SPICE. Tetapi kemampuan itu hanya diberikan untuk professional version, tidak bisa diakses dari student version atau demo version. Harga lisensi PSIM Professional tidaklah murah, karena itu saya mencari alternatif yang secara legal gratis untuk dipergunakan.

[ Semua gambar di bawah ini dapat dilihat versi tampilan yang lebih besar dengan cara melakukan klik-kanan di gambar lalu memilih “Open image in new tab” pada browser. ]

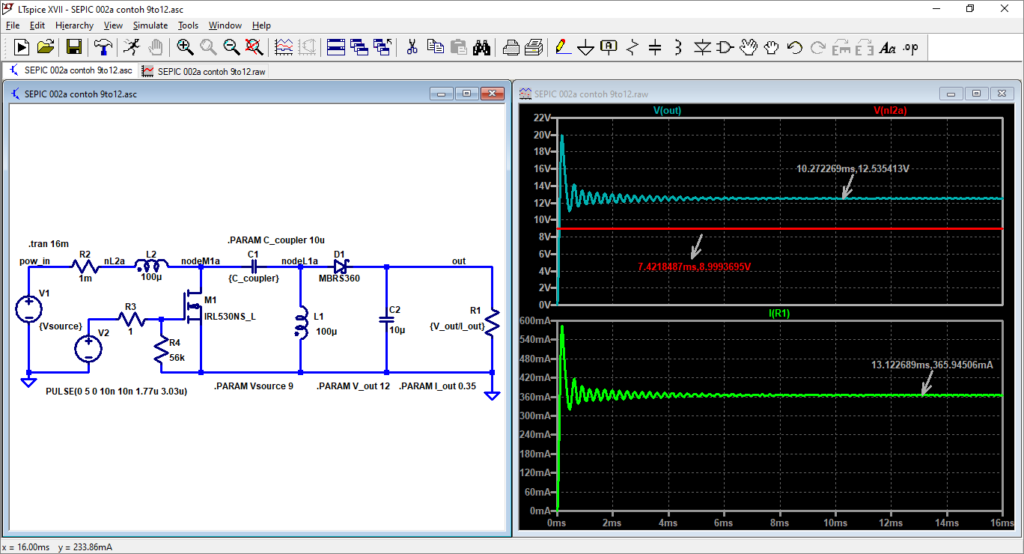

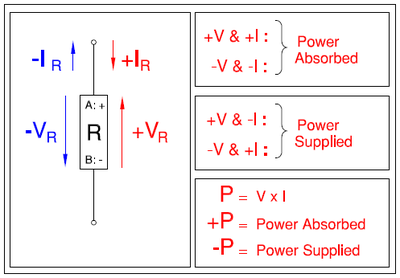

Gambar 1. Gambaran umum simulasi SEPIC di LTspice.

Gambar 1. Gambaran umum simulasi SEPIC di LTspice.

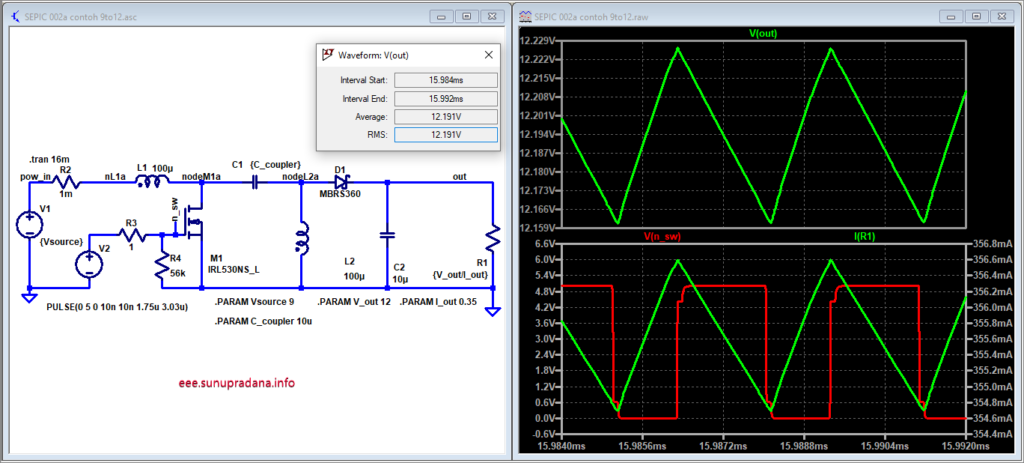

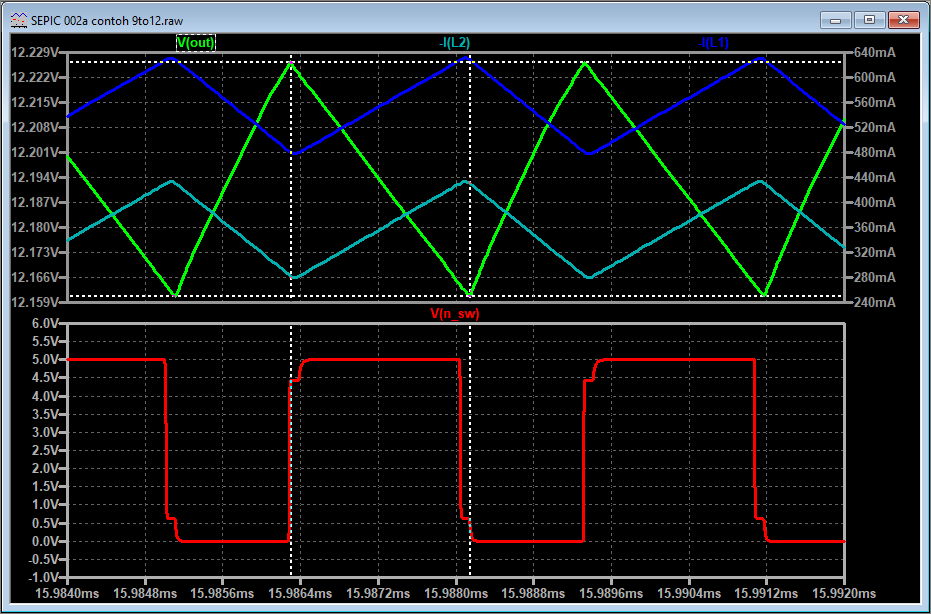

Gambar 2. Zoom-in hasil simulasi awal rangkaian, dengan LTspice.

Gambar 2. Zoom-in hasil simulasi awal rangkaian, dengan LTspice.

Dapat dilihat di Gambar 1 dan Gambar 2 bahwa pertama, terdapat ripple (riak) yang cukup besar di awal operasi (kondisi transient) bila dibandingkan dengan pada saat kondisi relatif stabil. Kedua, di Gambar 2 bisa dilihat bahwa sinyal/gelombang yang tampaknya rata di Gambar 1 baru akan terlihat riaknya dengan jelas jika dilakukan pembesaran (zoom). Ini adalah hal yang umum di semua produk DC-to-DC converter. Terutama, pada tipe catu daya tersakelar seperti itu ripple akan sulit dihindari. Yang bisa dilakukan hanyalah untuk memperkecil nilainya sedemikian rupa sehingga masih masuk ke dalam rentang nilai yang dapat diterima. Nilai ini biasanya tergantung pada beban dan aplikasinya (penggunaannya). Ketiga, bisa dilihat bahwa nilai arus dan tegangan keluaran dengan duty cycle yang sama seperti pada waktu simulasi dengan PSD dan PSIM akan memberikan hasil yang berbeda. Hal ini karena di simulasi LTspice ini, tidak lagi mempergunakan semua model komponen ideal. Tetapi sudah mempergunakan model komponen yang lebih mendekati komponen fisik.

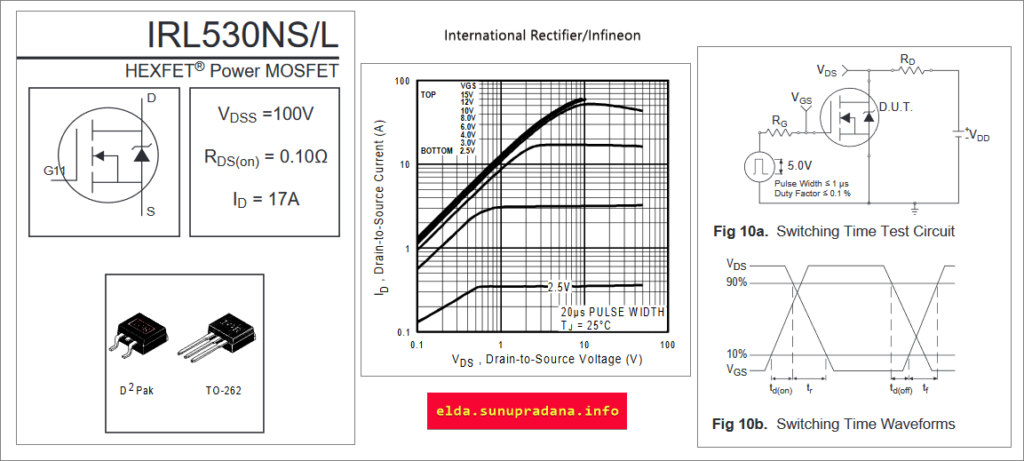

Sakelar elektronik berupa MOSFET yang dipergunakan dalam simulasi dengan LTspice ini adalah model komponen yang sudah tersedia sedari awal di LTspice XVII, sehingga tidak perlu menambahkan lagi model yang baru. Model komponen MOSFET yang dipergunakan adalah IRL530NS_L (IRL530NS/L). Komponen ini diproduksi oleh perusahaan asal Amerika Serikat, International Rectifier (www.irf.com) yang sekarang sudah digabung dengan perusahaan asal Jerman, Infineon Technologies AG (www.infineon.com). IRF sekarang menjadi Infineon Technologies Americas Corp. Datasheet untuk IRL530NS/L masih dapat ditemukan di sini.

Pemilihan model komponen yang akan dipakai di simulasi bergantung kepada beberapa hal. Misalnya secara praktis apa saja komponen yang tersedia di ‘pasaran’ yang mungkin dipilih. Ini penting karena sebaiknya tentu saja model komponen yang dipakai dalam simulasi sebaiknya adalah model dari komponen yang nanti akan benar-benar dipergunakan, diwujudkan dalam sistem fisik. Atau setidaknya model komponen yang karakteristiknya terdekat/dekat dengan komponen fisik yang akan dipakai.

Namum demikian, kadang-kadang urutan tersebut bisa berubah sesuai keperluan. Misalnya model komponen IRL530NS_L (IRL530NS/L) ini dipergunakan karena prioritas utama adalah menggunakan model SPICE yang sudah tersedia secara default di LTspice. Urutan prioritas berikutnya baru kemudian adalah diupayakan agar model SPICE komponen yang dipakai adalah yang bertipe logic level device MOSFET. Metode ini dipakai karena tujuan utama simulasi ini adalah untuk menunjukkan bagaimana LTspice dapat dipakai untuk menggantikan PSIM dalam melakukan simulasi rangkaian SEPIC.

Gambar 3. Bagian dari datasheet IRL530NS/L.

Gambar 3. Bagian dari datasheet IRL530NS/L.

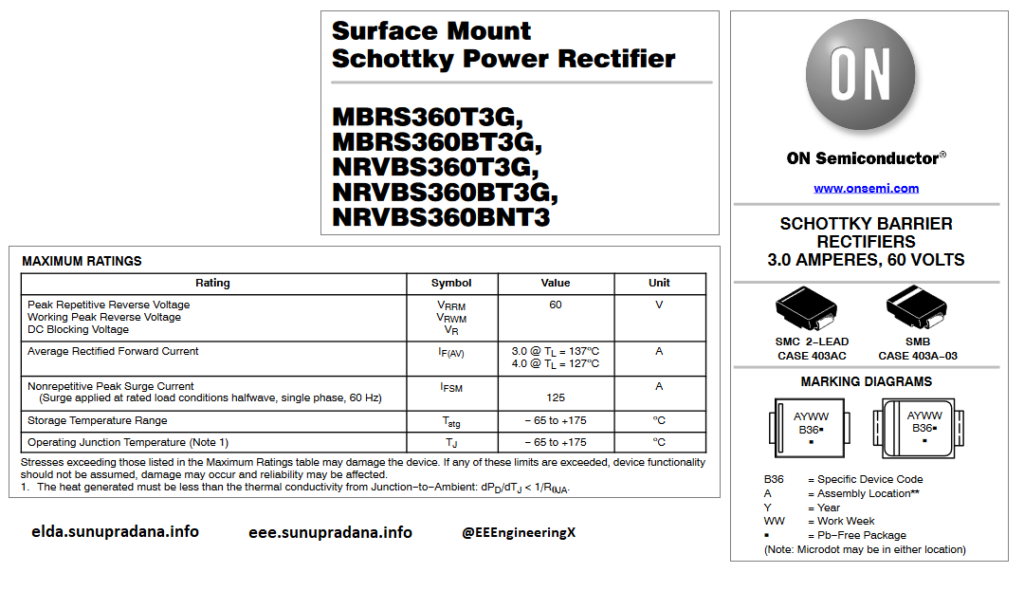

Untuk komponen sakelar diode, di simulasi LTspice ini saya mempergunakan model komponen diode Schottky MBRS360. Untuk sistem catu daya tersakelar (SMPS) harus mempergunakan diode yang dapat disakelar dengan cepat seperti diode Schottky.

Gambar 4. Kutipan dari datasheet diode Schottky yang dipakai dalam simulasi.

Gambar 4. Kutipan dari datasheet diode Schottky yang dipakai dalam simulasi.

Model komponen yang dipergunakan dalam simulasi haruslah dari komponen yang mampu untuk bekerja dengan tingkat tegangan, arus, dan frekuensi yang terdapat di sistem yang sedang/akan dismulasikan. Kita dapat melakukan penyesuaian dengan mengganti satu model komponen ke model yang lain yang lebih sesuai untuk rangkaian/sistem yang sedang disimulasikan. Misalnya komponen diode dapat diganti ke tipe yang mampu menangani arus yang lebih besar dan menahan tegangan balik yang lebih tinggi.

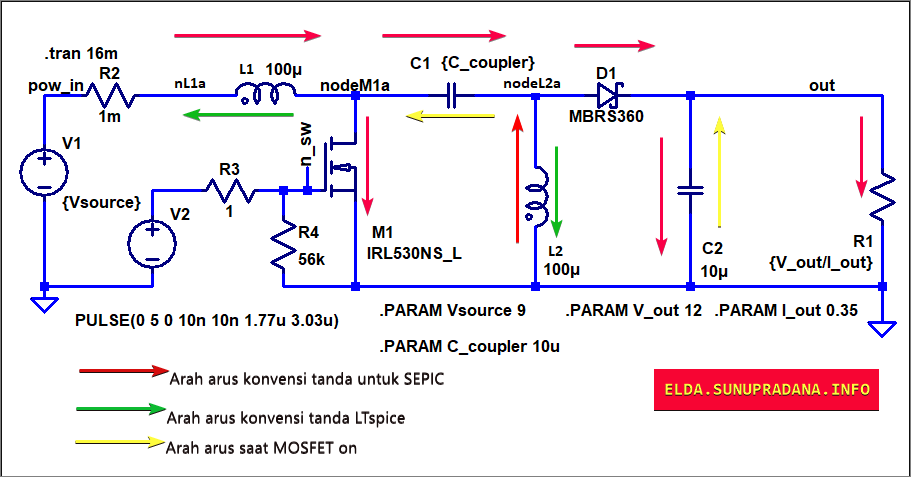

Gambar 5. Konvensi arah arus untuk simulasi SEPIC di LTspice.

Gambar 5. Konvensi arah arus untuk simulasi SEPIC di LTspice.

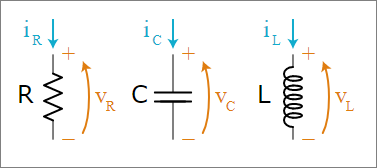

Gambar 5 diperlukan agar tidak salah memahami penandaan polaritas -/+ arus di LTspice. Ini dikarenakan cara penandaan arah arus yang berbeda di LTspice, misalnya, dengan PSIM. Tanda panah yang saya beri warna merah menandakan konvensi arah arus yang mengikuti pengaturan pada textbook; D. W. Hart, Power Electronics, 1st ed. New York: McGraw-Hill Higher Education, 2010. Arah ini hanya konvensi, arah arus sebenarnya untuk tiap saat pada simulasi tidak selalu sama dengan arah ini. Jika berlawanan, maka diberi tanda negatif. Jika sesuai diberi tanda positif, atau dalam praktik yang lebih umum tidak diberi tanda sama sekali. Bandingkan Gambar 5 di artikel ini dengan Gambar 15, Gambar 16, dan Gambar 17 di post sebelumnya.

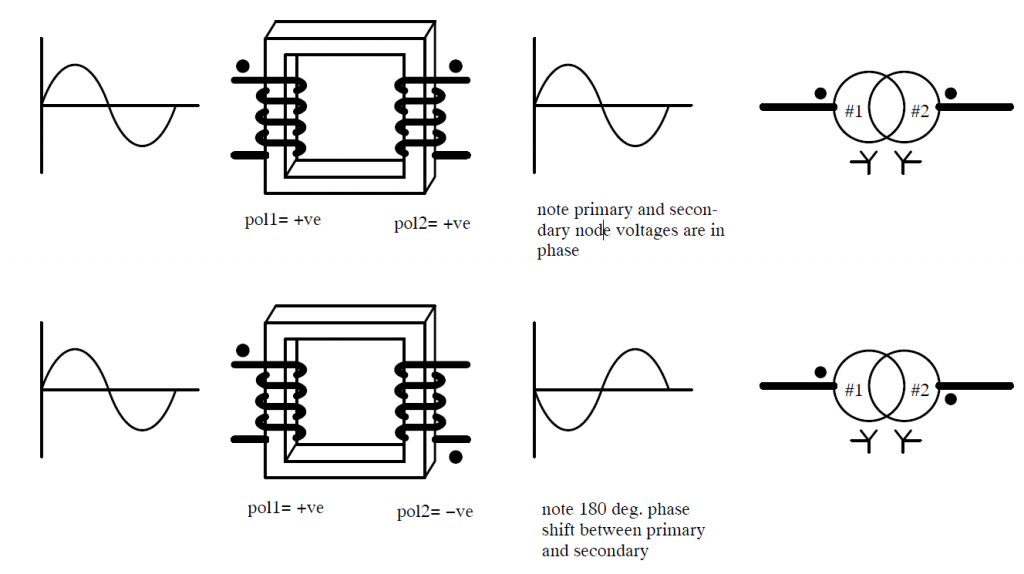

Komponen fisik resistor dan induktor tidak memiliki polaritas tegangan dan arus. Beberapa induktor (mutual inductance) diberi tanda titik (dot) untuk menunjukkan polaritas arus. Gambar 6 berikut ini menunjukkan bagaimana dot convention dipergunakan untuk menandai arah arus dan polaritas/fase pada tegangan di transformer.

Gambar 6. Dot convention dari circuitdigest.com.

Gambar 6. Dot convention dari circuitdigest.com.

Gambar 7 menunjukkan perwujudan fisik di transformer/mutual induction yang berkaitan dengan penandaan titik, dot convention.

Gambar 7. Contoh penerapan dot convention di trafo, menurut RTDS Technologies.

Gambar 7. Contoh penerapan dot convention di trafo, menurut RTDS Technologies.

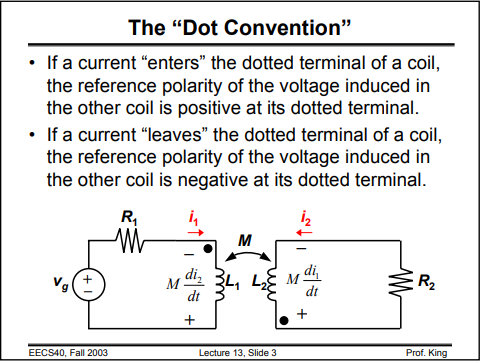

Gambar 8. Konvensi tanda titik (EECS Berkeley)

Gambar 8. Konvensi tanda titik (EECS Berkeley)

Gambar 9. Empat kemungkinan konfigurasi dot convention (The Citadel.edu).

Gambar 9. Empat kemungkinan konfigurasi dot convention (The Citadel.edu).

Jika tertarik untuk lebih jelas mengenai dot convention untuk mutual inductance, dapat melihat tiga video berikut ini; link 1, link 2, link 3.

Di simulator PSIM, passive sign convention diperjelas dengan pemberian tanda dot (titik) di setiap komponen pasif. Bisa kembali di lihat di Gambar 9 di artikel sebelum ini. Misalnya di induktor, arah arus akan selalu dianggap memasuki komponen dari arah tanda titik (dot). Jika arus pada saat pengukuran ternyata arah arus sebenarnya ternyata berlawanan, maka akan diberi tanda negatif. Jika ternyata bersesuaian (searah) maka akan dianggap positif (biasanya tanda + tidak dicantumkan).

Pengaturan yang berbeda dilakukan untuk komponen pasif di simulator LTspice. Misalnya sekalipun komponen fisik resistor tidak memiliki polaritas dan simbol resistor di LTspice pun tidak memiliki tanda dot, tetapi untuk memenuhi passive sign convention dan mempermudah pembacaan arah arus maka model komponen resistor di LTspice memiliki ‘polaritas’. Bagi pengguna yang belum terbiasa, arah arus yang melewati resistor bisa diketahui setelah melakukan simulasi pertama untuk rangkaian yang terdapat resistor tersebut. Jika konvensi arah arus dianggap tidak cocok, maka pengguna bisa melakukan rotate untuk mengubah konvensi arah arus yang melintasi resistor itu.

Hal yang sama juga berlaku untuk komponen kapasitor non-polar. Tipe kapasitor ini jelas sesungguhnya tidak memiliki polaritas. Tetapi untuk kepentingan simulasi, sama seperti resistor, bahkan komponen non-polar capacitor ini pun memiliki konvensi arah arus yang tetap. Sama seperti resistor, pengguna simulator dapat mengubah posisi kapasitor sehingga konvensi arah arus akan sesuai dengan kehendaknya. Jika nanti hasil pengukuran simulasi menunjukkan nilai arus negatif, maka itu artinya arah arus yang sebenarnya di simulasi berlawanan arah dengan konvensi arah arus yang ditetapkan (arah/posisi kapasitor terhadap node di rangkaian).

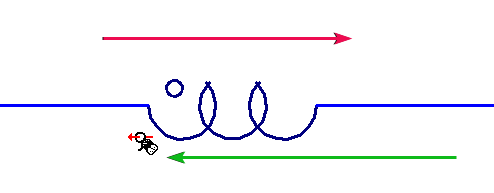

Pengaturan konvensi arah arus untuk induktor di PSIM mengikuti passive sign convention. Arus dianggap positif jika masuk ke induktor dari kaki yang bertanda titik (dot), dan diberi tanda negatif jika sebaliknya. Bisa dilihat kembali di Gambar 9 di post sebelumnya. Sedangkan pengaturan yang berbeda untuk simulasi di LTspice. Lihatlah Gambar 10 berikut ini, jika umumnya konvensi tanda pasif untuk induktor seperti panah berwarna merah, maka di LTspice justru mengikuti arah seperti panah berwarna hijau. Simulator PSIM menggunakan konvensi yang searah dengan panah berwarna merah di Gambar 10. Demikian juga untuk konvensi tanda rangkaian dasar SEPIC di buku Power Electronics tulisan Daniel W. Hart. Di LTspice jika kursor anda tempatkan di sekitar atas komponen maka akan muncul lambang current probe seperti di Gambar 10 ini.

Gambar 10. Konvensi penandaan arah arus untuk induktor di LTspice.

Gambar 10. Konvensi penandaan arah arus untuk induktor di LTspice.

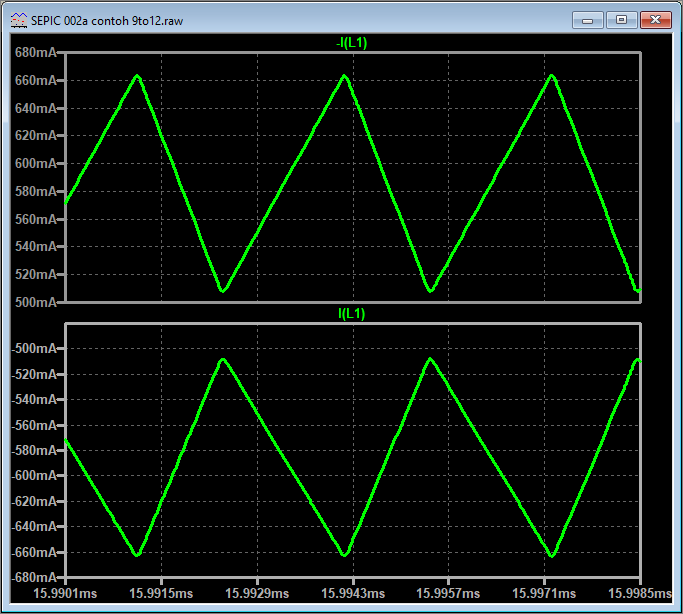

Maka ada beberapa alternatif solusi agar polaritas arus di simulasi LTspice dapat mudah dibaca dan bersesuaian dengan konvensi penandaan arus pasif. Pertama dengan memutar atau menggunakan efek cermin. Dengan cara ini, misalnya, tanda titik di induktor di Gambar 10 akan berada berpindah dari sebelah kiri ke sebelah kanan. Cara kedua adalah dengan menggunakan cara klasik keluarga simulator berbasis SPICE, yaitu dengan memasang sumber tegangan ideal. Caranya adalah dengan memasang sumber tegangan ideal secara seri dengan induktor. Arah induktor tidak diubah, tetapi hanya arah hadap (polaritas) sumber tegangan ideal saja yang disesuaikan. Sumber tegangan ideal yang akan berfungsi sebagai ampermeter itu diberi nilai 0 V. Cara ketiga yang paling mudah tanpa mengubah rangkaian adalah dengan mengganti polaritas sinyal hasil pengukuran. Misalnya dari I(L1) menjadi -I(L1), nilai absolutnya tidak akan berubah, hanya tandanya dan polaritas sinyalnya saja yang berubah. Lihatlah Gambar 11 berikut ini.

Gambar 11. Perbandingan sinyal/gelombang antara I(L1) dan -I(L1).

Gambar 11. Perbandingan sinyal/gelombang antara I(L1) dan -I(L1).

Gambar 12. Passive sign convention/sign convention for passive components (Khan Academy)

Gambar 12. Passive sign convention/sign convention for passive components (Khan Academy)

Gambar 13. Daya/power & passive sign convention (wikiversity.org)

Gambar 13. Daya/power & passive sign convention (wikiversity.org)

Gambar 12 dan Gambar 13 dapat dipergunakan untuk secara cepat mengingat kembali konvensi tanda / penandaan pasif, termasuk untuk sistem catu daya. Tanda positif dan negatif hanya dipergunakan dalam konteks arah, mengirim / menerima, memberi / menyerap.

Kembali ke Gambar 5 di bagian atas, kita akan mengikuti konvensi arah arus seperti di textbook Daniel W. Hart. Konvensi arah arus yang dijadikan patokan adalah yang berwarna merah. Pengaturan arah arus di induktor oleh LTspice yang ditandai panah berwarna hijau akan diatasi dengan mengalikan hasil pengukuran dengan -1 (membalik arah arus). Sedangkan arah arus di kapasitor yang berubah-ubah sesuai kondisi sakelar akan tetap mengikuti passive sign convention, karena untuk kapasitor pengaturan konvensi arah arus LTspice sudah sama. Misalnya pada saat sakelar MOSFET terbuka (tidak aktif/off) maka arah arus yang melewati kapasitor sama dengan arah tanda panah berwarna merah, dianggap positif. Sedangkan saat MOSFET tertutup, arah arus sebenarnya di kapasitor berbalik arah. Arahnya berlawanan dengan panah berwarna merah, di Gambar 5 ini ditandai dengan panah berwarna kuning.

Gambar 14. Pengaruh pemicuan pada arus dan tegangan di beban.

Gambar 14. Pengaruh pemicuan pada arus dan tegangan di beban.

Penandaan nama komponen di rangkaian di Gambar 14 telah diubah dari Gambar 1. Begitu pun nilai duty cycle telah diubah dari rancangan awalnya di PSD dan Gambar 1. Karena di LTspice rangkaian telah mempergunakan model komponen yang tidak lagi ideal, maka unjuk kerja komponen yang dimaksud pun menjadi berbeda. Penyesuaian seperti ini lazim dilakukan seiring perubahan penggunaan model komponen, parameter operasi, atau bahkan perubahan software simulator. Saat mewujudkan sistem secara fisik pun, fine tuning masih perlu dilakukan. Terutama untuk tipe open-loop, karena untuk closed-loop penyesuaian terus menerus saat kondisi operasi sudah diambil alih oleh regulator/controller.

Di Gambar 14 dapat dilihat bahwa arus dan tegangan di beban resistor adalah berbanding lurus, persis seperti yang digambarkan dalam hukum Ohm. Gambar 14 ini penting untuk sebagai awalan analisis unjuk kerja rangkaian berdasarkan kondisi penyakelaran. Di gambar ini secara sederhana dan jelas korelasi antara kondisi penyakelaran dengan kondisi arus dan tegangan di beban resistor. Ini akan dapat menjadi acuan yang mudah untuk telaah dan analisis pengaruh penyakelaran MOSFET pada kondisi komponen lain. Di sini juga bisa dilihat bahwa korelasi antara gelombang arus dan gelombang tegangan di beban adalah bersifat kausalitas dengan gelombang tegangan sebagai penyebab dan nilai electrical di beban sebagai akibat. Saat sakelar terpicu, MOSFET menutup, nilai arus dan tegangan di beban terlihat menurun. Sedangkan saat MOSFET membuka, nilai tegangan di beban justru naik. Kenapa ini terjadi? Jawabannya ada di bagian selanjutnya di bagian bawah artikel ini. Silakan melanjutkan membaca.

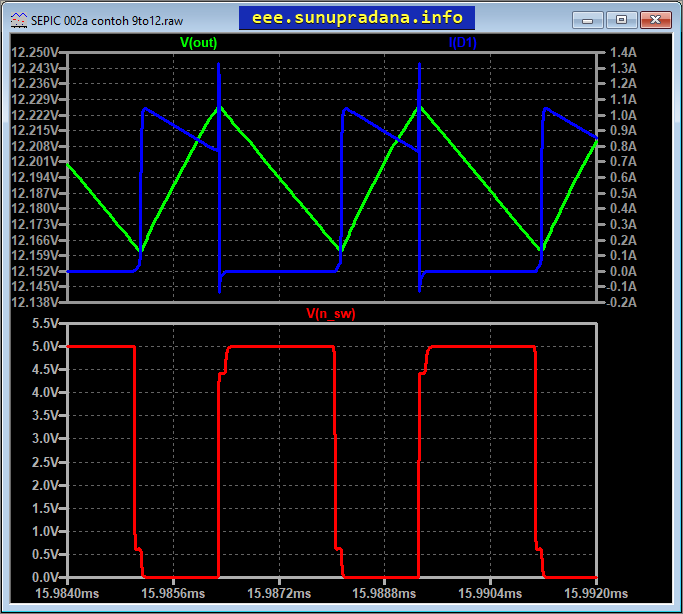

Gambar 15. Pengaruh pemicuan pada arus diode dan tegangan di beban.

Gambar 15. Pengaruh pemicuan pada arus diode dan tegangan di beban.

Di Gambar 15, di pane bagian bawah diperlihatkan nilai dan gelombang tegangan pemicu MOSFET, on and off level. Sedangkan plot pane di bagian atas menunjukkan gelombang tegangan di beban dan arus diode. Nilai tegangan keluaran (gelombang hijau) dibaca mengikuti sumbu Y di sebelah kiri, sedangkan nilai arus diode (gelombang berwarna biru) dibaca mengikuti sumby Y di sebelah kanan. Bisa dilihat dan dibaca secara sederhana bahwa saat MOSFET terpicu aktif / on maka arus diode secara praktis nol, sedangkan pada saat MOSFET membuka diode mengalirkan arus (diode aktif menghantar). Ini adalah contoh analisis yang bertahap mulai dari yang paling sederhana. Di bagian selanjutnya di bawah ini akan dibahas ulang dengan lebih detail. Untuk sekarang, yang paling penting kita paham gejala hubungan antara sinyal tegangan pemicuan sakelar, sinyal arus di diode, dan sinyal tegangan di beban.

Gambar 16. Pengaruh pemicuan pada arus di kedua kapasitor dan tegangan di beban.

Gambar 16. Pengaruh pemicuan pada arus di kedua kapasitor dan tegangan di beban.

Fokus di Gambar 16 adalah arus di kapasitor, dan bagaimana hubungannya dengan sinyal tegangan pemicuan sekelar MOSFET dan sinyal tegangan keluaran di beban resistor. Dapat dilihat bahwa arus di kedua kapasitor itu berbanding lurus. Kemudian dapat dilihat juga bahwa arus di kedua kapasitor itu memiliki nilai negatif dan positif. Ini artinya bahwa ada saat arus di kedua kapasitor itu berbalik arah. Arus negatif hanya berarti arahnya berlawanan dengan konvensi penandaan arah arus, demikian juga sebaliknya. Saat MOSFET menutup, arus keluar dari kapasitor. Saat MOSFET membuka, arus masuk ke kapasitor.

Untuk tulisan ini dan banyak pembahasan di artikel saya yang lain, saat menyebut arus di kapasitor maka yang dimaksud adalah dalam konteks analisis rangkaian yang praktis. Di dalam fisik komponen kapasitor terdapat bagian isolator yang dinamakan dielectric. Karena itu jika ingin mengetahui lebih jauh dari sekadar pemahaman praktis tentang aliran arus di kapasitor, silakan mencari keterangan tambahan dengan mempergunakan search engine seperti Google atau Bing. Sebagai awalan, gunakan kata-kata kunci displacement current dan Maxwell’s equations.

Gambar 17. Pengaruh pemicuan pada arus di kedua induktor dan tegangan di beban.

Gambar 17. Pengaruh pemicuan pada arus di kedua induktor dan tegangan di beban.

Gambar 17 dibuat untuk memfokuskan perhatian ke kondisi arus di kedua komponen induktor dalam rangkaian SEPIC. Pembacaan pola gelombang ini dilakukan dengan tetap menjadikan sinyal pemicuan MOSFET dan sinyal tegangan keluaran sebagai patokan acuan. Yang paling mudah dilihat adalah bahwa nilai arus di kedua induktor berbanding lurus. Ini adalah korelasi tetapi bukan hubungan kausalitas. Kedua sinyal itu dipicu oleh kerja/aktivitas MOSFET. Kemudian bisa diperhatikan adalah bahwa polaritas arus di kedua induktor tetap. Ini artinya arah arus di semua induktor itu tetap, dan searah dengan konvensi tanda arah arus. Berikutnya bisa dilihat bahwa gejala arus di semua konduktor berbanding terbalik dengan nilai tegangan di beban. Saat MOSFET aktif, besar arus di kedua induktor bertambah, tetapi justru nilai tegangan beban menurun (yang secara implisit artinya bahwa nilai arus ke beban resistor itu juga menurun). Sebaliknya saat MOSFET non-aktif, besaran arus di kedua induktor mengalami penurunan, tetapi justru nilai (arus dan) tegangan di beban resistor meningkat. Mengapa ini terjadi? Adakah penjelasan yang lebih dalam? Coba lanjutkan baca bagian di bawah ini.

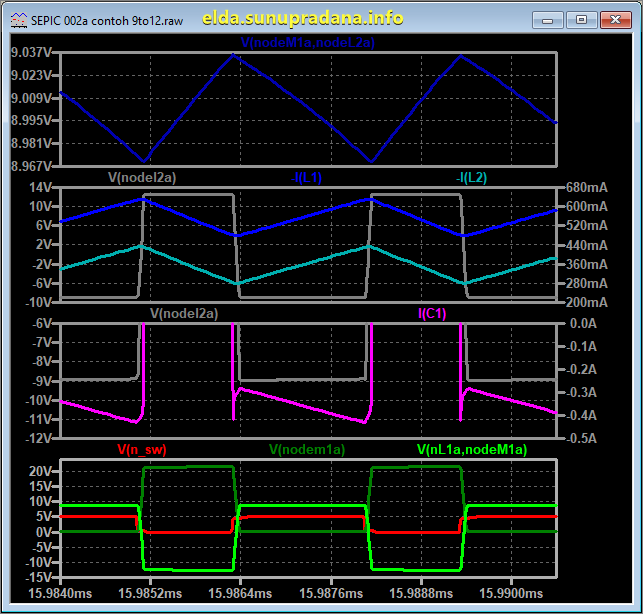

Gambar 18. Simulasi dengan fokus pengaruh MOSFET on pada kondisi arus dan tegangan di tiap komponen.

Gambar 18. Simulasi dengan fokus pengaruh MOSFET on pada kondisi arus dan tegangan di tiap komponen.

Jika anda membuka Gambar 5 di new tab atau new page, anda akan lebih mudah memahami pembacaan gejala sinyal di Gambar 18. Di gambar ini, nodel2a (nodeL2a) sengaja dimunculkan dua kali di plot pane yang berbeda. Di pane bagian atas, ditampilkan gambar gelombang tegangan yang utuh di node nodel2a, yaitu dari -8.9 V sampai 12.5 V. Sedangkan di pane di bagian bawah tegangan di node nodel2a hanya diatur untuk menampilkan bagian gelombang yang negatif saja.

Saat MOSFET aktif/on maka tegangan di node nodeM1a secara praktis adalah 0 V (tepatnya di bawah 80 mV akibat ketidakidealan MOSFET), karena dihubungkan dengan ground. Saat itu aliran arus yang melintasi L1 meningkat, dari titik nilai arus terendahnya menuju ke titik nilai arus tertingginya. Dengan pertambahan arus, maka nilai tegangan di induktor L1 juga meningkat. Jika ketidakidealan sementara dapat dikesampingkan maka nilai tegangan di L1 akan sama dengan nilai tegangan di sumber, yaitu 9 V. Ini karena saat sakelar MOSFET menutup, secara praktis L1 terhubung paralel dengan sumber tegangan ideal.

Saat MOSFET aktif/on maka kapasitor C1 akan terhubung paralel dengan induktor L2. Seandainya dalam kondisi ideal maka nilai tegangan di (kaki-kaki) L2 akan sama persis dengan nilai tegangan di (kaki-kaki) C1. Di Gambar 18, gelombang tegangan di C1 ada di pane paling atas, karena posisi C1 ada di antara nodeM1a dan nodeL2a. Nilai maksimumnya sekitar 9 V, sama dengan nilai tegangan masukan. Sedangkan posisi L2 berada antara nodeL2a dan ground. Rantang nilai tegangannya adalah -8.9 V sampai 12.5 V. Di pane kedua dari bawah, sengaja diatur agar kita bisa fokus melihat gelombang tegangan di nodeL2a dalam rentang negatifnya. Di sana bisa dilihat bahwa nilai tegangan di L2 (nodeL2a-gnd) saat sakelar MOSFET on adalah sekitar -8.9 V. Ini adalah nilai tegangan di kapasitor C1, bukti bahwa pada kondisi ini C1 dan L2 secara praktis terhubung paralel. Dengan mengingat dan memperhatikan KVL, maka nilai tegangan di loop tertutup C1 dan L2 adalah nol volt. Anda bisa lihat di hasil simulasi di Gambar 18 bahwa pada saat ini nilai V(nodel2a) bahkan negatif terhadap acuan ground. Karena itu dapat mudah dipahami bahwa pada kondisi sakelar MOSFET tertutup ini, diode D1 dalam keadaan terbuka / tidak menghantar. Nilai tegangan V(out) terhadap ground adalah sekitar 12.1 V. Tetapi nilai node di sisi anode D1 adalah -21.1 V terhadap sisi katodenya. Sisi katode D1 adalah node yang sama dengan node out beban (lihat Gambar 5).

Saat MOSFET aktif/on arah arus yang sebenarnya di C1 berlawanan dengan konvensi arah arus, karena itu diberi tanda negatif. Arah arus yang sesungguhnya adalah keluar dari kapasitor C1 menuju MOSFET kemudian lanjut menuju L2 untuk kembali lagi ke kapasitor melalui kaki C1 yang berbeda. Polaritas tegangan di C1 tidak berubah, hanya saja nilainya menurun/berkurang. Ini dikarenakan pada saat inilah kapasitor C1 mengeluarkan energi yang disimpannya dalam bentuk medan listrik melalui arus yang akan menambah cadangan energi di L2. Dengan kata lain, secara informal, C1 sedang membuang muatan ke L2.

Gambar 19. Pengaruh MOSFET on dan MOSFET off pada kondisi arus dan tegangan di tiap komponen.

Gambar 19. Pengaruh MOSFET on dan MOSFET off pada kondisi arus dan tegangan di tiap komponen.

Gambar 19 ini pada dasarnya hampir sama dengan Gambar 18. Hanya saja Gambar 18 difokuskan untuk kondisi MOSFET on, sedangkan gambar terakhir ini untuk kondisi sakelar MOSFET off yang sebenarnya lebih mudah untuk dipahami. Dimulai saat tingkat tegangan pemicuan MOSFET turun ke nol volt. Maka saat itulah tegangan dan arus di beban menuju nilai maksimum. Bagaimana ini bisa terjadi?

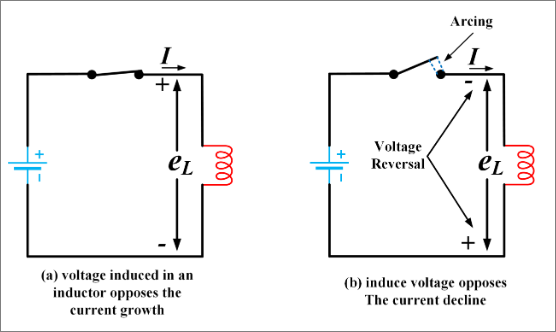

Saat MOSFET membuka ini, nodeM1a tidak lagi terhubung ‘langsung’ dengan node ground (agar lebih mudah lihat Gambar 5 di new tab atau di new window). Polaritas konduktor L1 berbalik tanda dari tadinya positif menjadi sekarang negatif. Jika anda lupa dengan efek back EMF, lihat kembali Gambar 20 (a) berikut ini.

Gambar 20. Perubahan polaritas di induktor (electricalacademia)

Gambar 20. Perubahan polaritas di induktor (electricalacademia)

Berbeda dengan tegangan di L1, sekalipun tegangan di L2 juga berbalik tanda, tetapi arah perubahannya berbeda. Perlu juga diingat bahwa kedua kaki konduktor L1 pada dasarnya ‘mengambang’. Hanya saat MOSFET aktif saja salah, satu kakinya akan terhubung ke ground. Kondisi koneksi L1 ini tidak sama dengan L2 yang salah satu kakinya selalu terhubung ke node acuan ground. Untuk konvensi arah tanda lihatlah Gambar 5.

Di Gambar 19 terlihat bahwa tegangan di nodeL2a yang tadinya negatif terhadap ground saat MOSFET aktif, sekarang menjadi bernilai positif terhadap ground saat MOSFET non-aktif. Sebelum melanjutkan, perlu dipahami lagi bahwa penempatan dan pengaturan arah polaritas model komponen L2 berbeda dengan L1 (lihat Gambar 5). Tetapi pada keduanya terjadi pembalikan polaritas sebagaimana seharusnya.

Jika nodeL2a menjadi lebih positif sekitar 12.5 V daripada gnd, artinya bahwa saat MOSFET off polaritas tegangan di L2 berbalik tanda. Saat ini diode D1 yang tadinya off menjadi on, mengalirkan arus dari nodeL2a ke node out. Arah arus L2 tetap dari sisi kaki node gnd ke nodeL2a.

Di Gambar 19 bisa dilihat bahwa apa pun kondisi penyakelaran MOSFET, polaritas (arah) arus di kedua konduktor tidak pernah berubah. Hanya besaran nilainya saja yang bertambah atau berkurang. Karena itu kondisi polaritas trend arus di L1 dan L2 sama.

Saat MOSFET off ini, nilai tegangan di kapasitor C1 menurun. Tetapi polaritas tegangan di kapasitor C1 tidak pernah berubah, bisa di lihat di plot pane nomor dua dari atas di Gambar 19. Tetapi arah arus di C1 yang justru berbalik, sekarang menjadi positif karena arus masuk dari L1 ke C1. Arus ini kemudian dari C1 akan melalui D1 menuju C2 dan beban.

Sama halnya dengan kapasitor C2 yang satu kakinya terhubung ke ground dan satu lagi terhubung ke node out. Bisa dilihat di Gambar 5 bahwa posisi C1 adalah benar-benar paralel dengan beban R1. Di saat MOSFET off ini, nilai tegangan di kapasitor C2 juga menurun. Tetapi polaritas tegangannya pun (kapasitor C2) tidak pernah berubah, bisa di lihat di plot pane paling atas di Gambar 19 (node out). Tetapi sama dengan C1, arah arus di C2 yang justru berbalik. Sekarang menjadi positif karena arus masuk dari L1 (melewati C1) ditambah arus masuk dari L2, keduanya melalui D1 menuju C2 (dan R1).

Masihkah ingat ‘eLi the iCe man’ dan teman-temannya? Dari operasi sistem rangkaian SEPIC ini, pelajaran yang mendasar (fundamental) kembali menunjukkan arti pentingnya.

Komponen inductor memiliki sifat utama inductance di samping sifat parasitic lainnya. Komponen ini menyimpan energi dalam bentuk medan magnet. Induktor melawan perubahan arus dengan cara menyimpan atau mengeluarkan energi dalam bentuk arus. Dalam operasi SEPIC ini bisa diperhatikan bahwa sesuai sifatnya, polaritas / arah arus induktor tidak pernah berubah tanda. Induktor bahkan ‘berusaha’ mempertahankan nilai besaran arus. Tetapi, polaritas tegangan induktor yang justru berubah tanda sebagai bagian dari upaya untuk mempertahankan arah dan besar arus. Perubahan ini terlihat jelas di Gambar 20.

Berkebalikan dan komplementer dengan induktor adalah komponen kapasitor. Komponen capacitor memiliki sifat utama capacitance di samping sifat parasitic lainnya. Komponen ini menyimpan energi dalam bentuk medan listrik. Kapasitor melawan perubahan tegangan juga dengan cara menyimpan atau mengeluarkan energi dalam bentuk arus. Dalam operasi SEPIC ini bisa diperhatikan bahwa sesuai sifatnya, polaritas / arah tegangan kapasitor tidak pernah berubah tanda. Kapasitor bahkan ‘berusaha’ mempertahankan nilai besaran tegangan di node dengan cara menyimpan kelebihan tegangan atau menambahi level tegangan. Tetapi, polaritas arus kapasitor yang justru berubah tanda sebagai bagian dari upaya untuk mempertahankan polaritas dan besar tegangan.

Kita juga bisa memperhatikan mengapa justru pada saat MOSFET dalam kondisi on, nilai arus dan tegangan di beban justru menurun/berkurang? Saat MOSFET aktif / menutup itu, justru beban hanya mendapat pasokan arus dari kapasitor C2. Kapasitor ini berusaha mempertahankan tingkat tegangan di node out yang juga salah satu node keluaran beban R1. Beban R1 yang paralel dengan C2 terpisah dari bagian rangkaian lainnya karena saat MOSFET menutup ini D1 akan terbuka / tidak aktif. Alasan detailnya telah dijabarkan di paragraf sebelumnya.

Sedangkan saat MOSFET off, beban R1 mendapat pasokan energi dari L1 dan L2 yang saat MOSFET on telah berkesempatan untuk menambah cadangan energinya. Karena itu pada saat MOSFET tidak aktif inilah justru nilai arus dan tegangan di beban berada pada nilai yang paling besar.

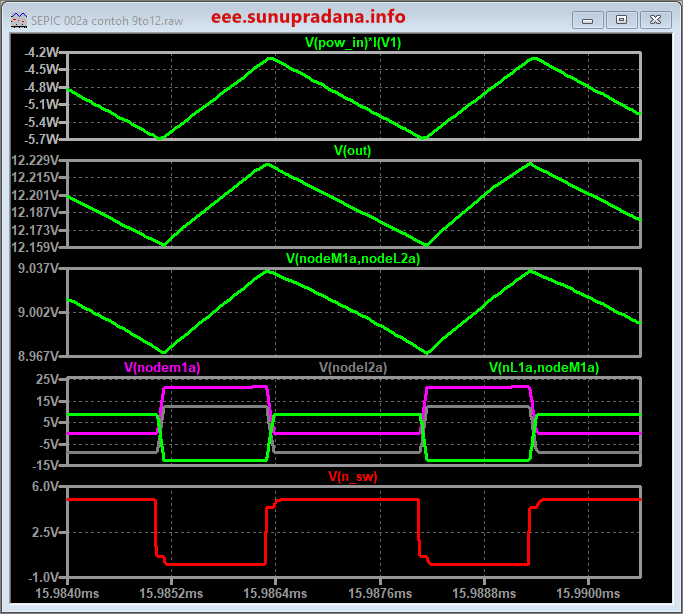

Gambar 20 menunjukkan bahwa nilai daya terbesar yang disalurkan adalah pada saat MOSFET aktif. Karena pada saat inilah sumber tegangan ideal memberikan energi dalam bentuk arus ke L1 untuk disimpan dalam bentuk medan magnet oleh induktor tersebut. Pengaturan siklus penyimpanan dan pengosongan energi ini diatur dengan mempergunakan nilai duty cycle. Tanda negatif pada daya di sumber tegangan adalah karena LTspice mempergunakan passive sign convention, lihat kembali Gambar 13.

Gambar 21. Power dissipation di sumber tegangan ideal.

Gambar 21. Power dissipation di sumber tegangan ideal.

font cache: Ψ α β π θ μ Φ φ ω Ω ° ~ ± ≈ ≠ ≡ ≤ ≥ ∞ ∫ • ∆